A Fondo

Vía libre para PCIe 6.0, la interfaz para el futuro del PC

PCI-SIG sigue dando pasos para el lanzamiento de PCIe 6.0, con la presentación del «Borrador completo» que definirá la nueva versión de un estándar destinado a dominar por completo la arquitectura de los PCs, del presente y del futuro.

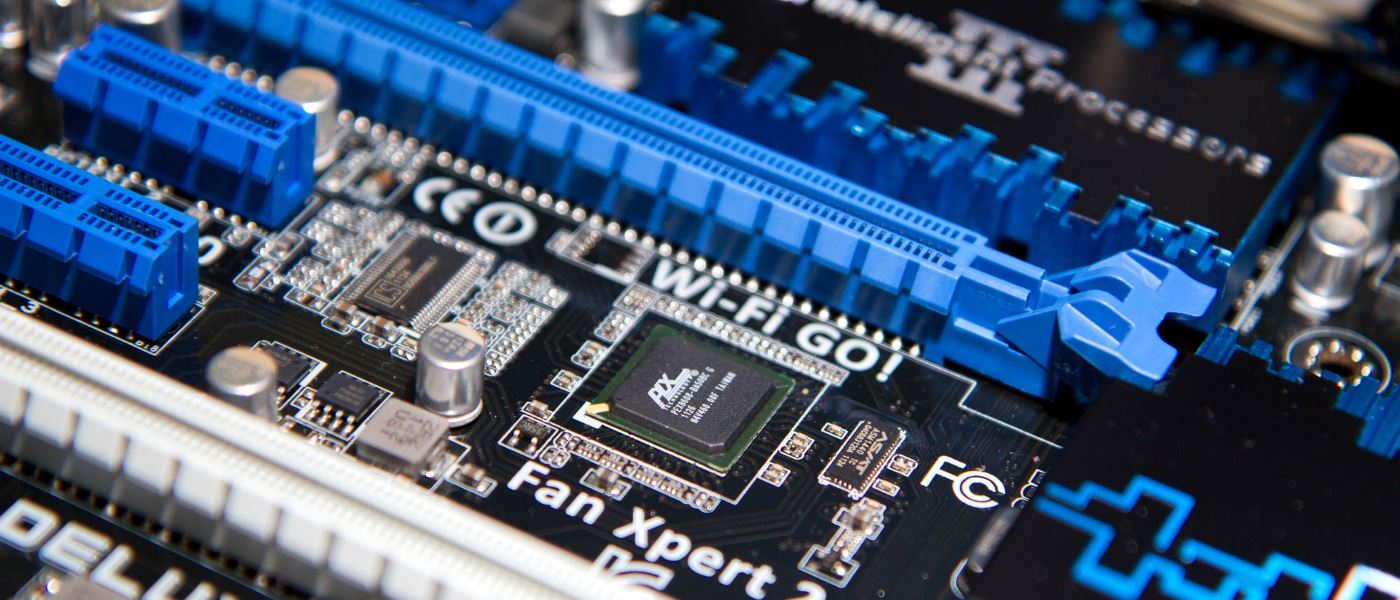

Ya conoces la importancia de PCI Express, un bus local de Entrada/Salida que verás abreviado como “PCI-E” o “PCIe” y que se ha convertido en fundamental en la arquitectura actual de las computadoras, una vez que “Grupo de Interés Especial de PCI” (PCI-SIG), una organización de 750 miembros donde están representados todos los grandes de la industria tecnológica, se marcó el objetivo de desarrollar un estándar único que reemplazara a buses anteriores como ISA, AGP o el mismo PCI en el que está basado.

Se utiliza tanto para conexión interna en los circuitos integrados de las placas base (chipsets) y la comunicación de componentes como CPU, como para conectar tarjetas externas pinchadas en los slots correspondientes. Es imprescindible para la instalación de tarjetas gráficas dedicadas, pero también puede usarse para conectar componentes de red, de sonido o de almacenamiento para instalar las SSD más rápidas del mercado.

El problema actual, como sucede con otros estándares, es que los distintos intereses de la industria ha provocado una acumulación de versiones que realmente no sabemos como se va a solventar. Si PCI 3.0 es todavía mayoritario, PCIe 4.0 se está extendiendo rápidamente una vez que -por fin- Intel se ha unido a AMD en su soporte. Quizá el retraso de Intel ha provocado esta acumulación y la hoja de ruta de los siguientes complicará la situación. La norma PCIe 5.0 también está completada y se cree que Intel lo estrenará en servidores el año próximo. Y PCIe 6.0 sigue avanzando.

PCIe 6.0: hoja de ruta

PCI-SIG ha publicado esta semana la versión 0.7 de la especificación. Esta versión es particularmente importante porque se trata del «Borrador completo» de la norma. Es decir, el estándar se ha definido por completo y ya no podrán añadirse nuevas características, mientras que las especificaciones eléctricas se han validado utilizando chips de prueba.

En la práctica, significa que PCIe 6.0 está listo y es funcional, por lo que es solo cuestión de tiempo antes de que se publique el borrador final (versión 0.9) con revisiones internas para su propiedad intelectual y patentes y la versión final (1.0). Ya en esta etapa, los fabricantes pueden tener implementaciones reales del nuevo bus listas, aunque no necesariamente anunciadas. No creemos que tarden en presentar los primeros desarrollos en fase de prototipo.

Teniendo en cuenta la situación del mercado actual, donde en la práctica PCIe 3.0 domina de manera amplísima, las PCIe 4.0 solo están en la fase inicial de despliegue y aún falta la comercialización de PCIe 5.0, no esperamos la nueva norma hasta 2023 / 2024 una vez que el año próximo la organización responsable publique las especificaciones finales. Obviamente, la hoja de ruta de PCIe está retrasadísima sobre lo esperado.

PCIe 6.0, novedades

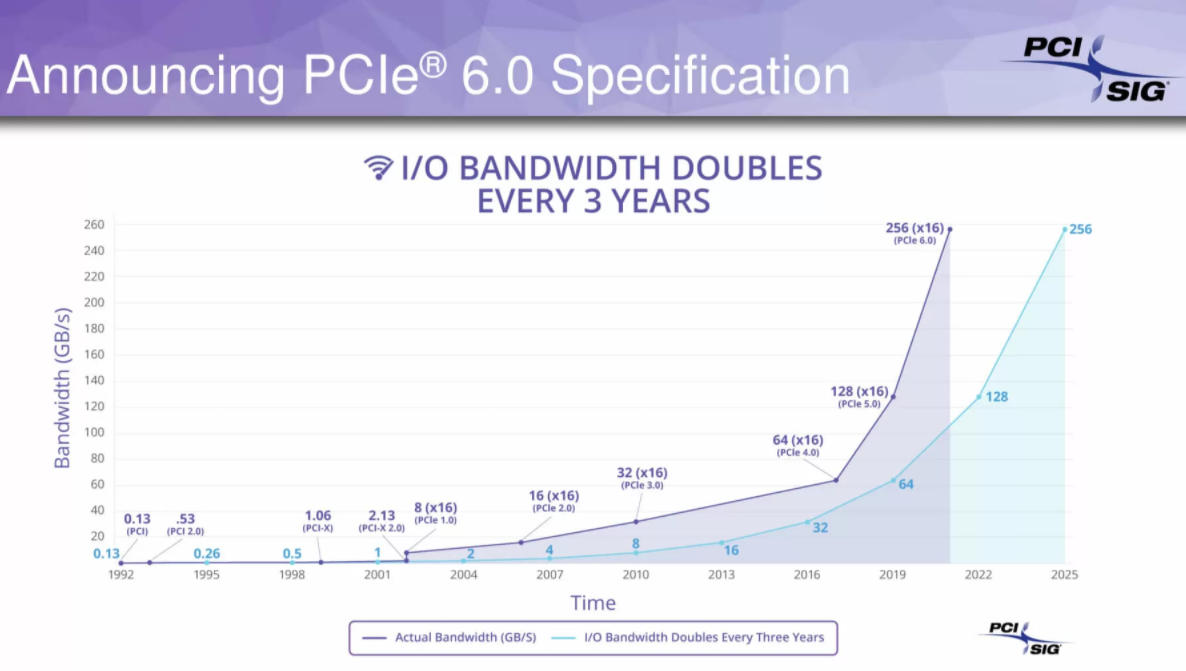

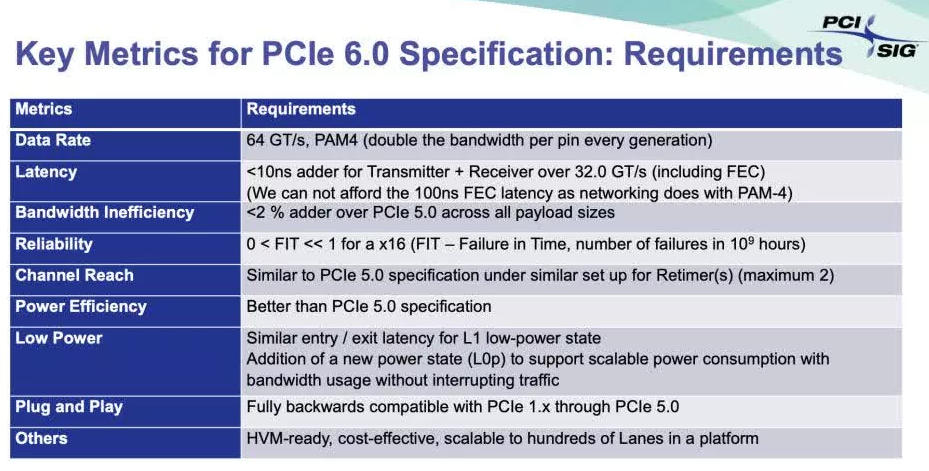

El principal avance de PCI Express 6.0 sobre las anteriores versiones del estándar será un aumento de rendimiento sustancial hasta alcanzar un ancho de banda de 256 GB/s en full duplex, duplicando el de PCI Express 5.0 y a su vez cuadriplicando el de PCI Express 4.0. Con una frecuencia de 64 Ghz, podrá ofrecer hasta 64 Gigatransferencias por segundo.

Además del aumento de rendimiento, una menor latencia, capacidades superiores RAS o mejora de la virtualización de E / S para acometer el aumento de necesidades de la industria, la nueva interfaz cambia el esquema de codificación a PAM4 para ayudar a aumentar las tasas de transferencia. El esquema se usa ampliamente en las redes de mayor rendimiento como las InfiniBand y también en la memoria GDDR6X.

En cuanto al alcance del canal, es decir, la «distancia» que puede recorrer la misma, sigue siendo similar al de la interfaz PCIe 5.0 y es fundamental para garantizar una amplia aceptación de la industria. El PCI-SIG no proporciona una medida de distancia específica para el alcance del canal, sino que especifica la cantidad de pérdida de señal tolerable, que permanece en 36dB para PCIe 6.0.

Otra de las mejoras llegará del menor tamaño físico del bus, lo que debe permitir la producción de tarjetas más pequeñas y no los monstruosos tamaños que podemos encontrar -por ejemplo- en las gráficas dedicadas de gama alta actuales.

En cuanto al lanzamiento ya hemos explicado que la norma llegará con bastante retraso sobre lo previsto. Ahora mismo, seguimos recomendando plataformas compatibles PCIe 4.0 a la hora de comprar equipos nuevos por su potencial de futuro, pero más allá no podemos ir de momento porque PCIe 5.0 apunta a estrenarse en el segmento de servidores y no en consumo y no llegaría al menos hasta 2022 con los Alder Lake-S (12ª Generación Core).

Si te pierdes con este estándar, te recomendamos la lectura de alguna de nuestras guías donde revisamos sus versiones, tipos y características:

- PCI Express, un bus único para el futuro del PC

- PCIe 4.0 frente a PCIe 3.0 ¿Hasta dónde llegan las mejoras en juegos?

-

NoticiasHace 7 días

NoticiasHace 7 díasPS6 Lite, una consola de nueva generación por 399 dólares

-

AnálisisHace 3 días

AnálisisHace 3 díasXteink X4: el ebook que no compite con tu Kindle sino con tu móvil

-

A FondoHace 6 días

A FondoHace 6 días16 GB de DDR5 en un módulo frente a 32 GB de DDR5 en dos módulos: ¿vale la pena montar solo un módulo de RAM?

-

NoticiasHace 5 días

NoticiasHace 5 díasRPCS3 ya funciona casi como una PS3 real: permite cargar juegos en ISO cifrado