Noticias

Zen 2 tiene el doble de memoria caché L3: ¿qué supone esto?

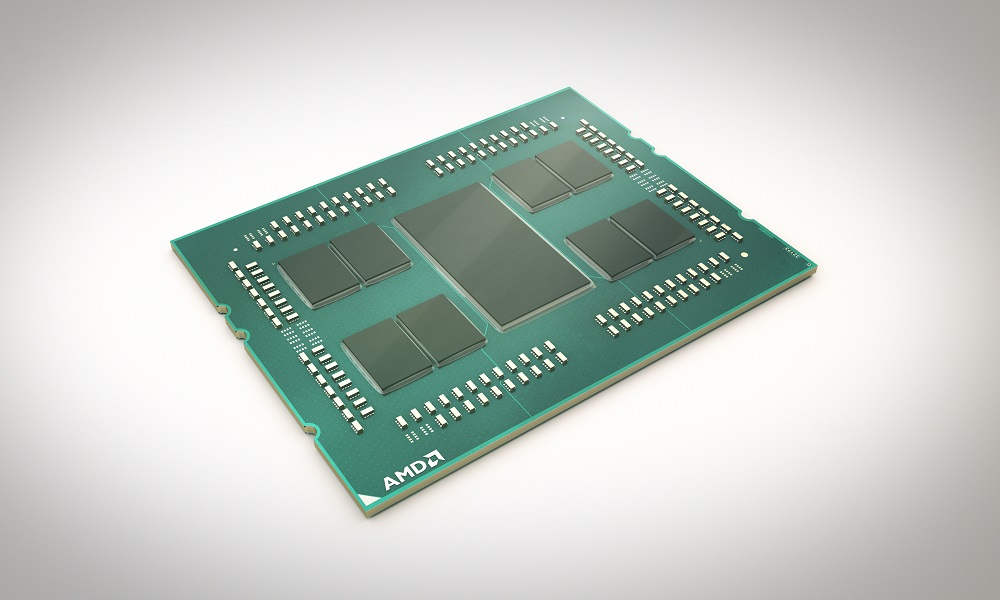

Una filtración aparecida en la base de datos de Sisoft SANDRA recoge un detalle muy interesante sobre la arquitectura Zen 2 que desconocíamos, y es que AMD ha doblado la cantidad de memoria caché L3 disponible en cada unidad CCX.

Hace algunas semanas hicimos un artículo especial donde hablamos de todas las cuestiones clave relacionadas con Zen 2. Sabíamos que esta nueva generación va a mantener el diseño MCM, es decir, que AMD repite su apuesta por el módulo multi-chip en detrimento del diseño de núcleo monolítico.

Bajo ese esquema tenemos un conjunto de bloques de núcleos en diferentes pastillas de silicio que se unen para trabajar al unísono. Cada pastilla de silicio suma un máximo de 8 núcleos y está fabricada en proceso de 7 nm. De la coordinación y de todos los elementos I/O necesarios se ocupa una solución fabricada en proceso de 14 nm que va ubicada en el centro del procesador, y comunica con todos los chiplets a través de un sistema Infinity Fabric mejorado.

Cambios muy importantes, ya que AMD ha decido además mover la controladora de memoria fuera de los chiplets, lo que ha simplificado aún más el proceso de fabricación y ha contribuido a reducir los costes, y ha permitido como dijimos doblar la cantidad de memoria caché L3 disponible por cada unidad CCX.

Según el listado que ofrece Sisoft SANDRA un procesador EPYC Rome (Zen 2) de 64 núcleos y 128 hilos tiene 256 MB de memoria caché L3, lo que se traduce en un total de 32 MB de caché L3 por cada grupo de chiplets. Sin embargo es importante matizar que la información que vemos en la captura de pantalla establece una diferenciación muy clara: 16 x 16. Esto quiere decir que en cada chiplet de ocho núcleos hay dos bloques de 16 MB de caché L3 cada uno, y que por tanto un chiplet está compuesto de dos unidades CCX de cuatro núcleos que comparten 16 MB de caché L3.

¿Qué ventajas ofrece tener una mayor cantidad de caché L3?

En este artículo hablamos de los componentes básicos de un procesador, y en él os explicamos todas las bases de la memoria caché. Zen 2 es una arquitectura MCM, así que su rendimiento depende en gran medida del sistema de comunicación que se utiliza para unir al grupo de chiplets, y también de la velocidad de la memoria RAM y de la capacidad y latencia de las cachés.

Contar con una memoria caché L3 de mayor tamaño podría ayudar a reducir el impacto de la memoria RAM en el sistema, y también a mejorar el rendimiento global bajo el nuevo sistema de I/O unificado en un único encapsulado central.

Gracias a esta información podemos hacer una colación directa a la estructura que podría adoptar AMD en sus procesadores Ryzen 3000 basados en Zen 2, y la conclusión es simple: los modelos de 8 núcleos tendrían 32 MB de caché L3. Si se confirma un nuevo tope de gama (Ryzen 7 3700X) con 16 núcleos y 32 hilos su memoria caché L3 ascendería bajo esta nueva arquitectura a 64 MB.

-

PrácticosHace 5 días

PrácticosHace 5 díasCómo montar archivos ISO (u otros formatos) en Windows

-

A FondoHace 11 horas

A FondoHace 11 horasLos 10 mejores reproductores de vídeo para Android (gratis y sin publicidad)

-

GuíasHace 4 días

GuíasHace 4 díasQué son los DNS y por qué mejoran la experiencia en Internet

-

PrácticosHace 3 días

PrácticosHace 3 díasSeis usos de un pendrive USB más allá de almacenar archivos